IBM 1130 PANEL UPGRADE

In addition to the two swapped thyristor and output socket components, I found that some of the 2 pin headers, which align the lamps to the holes in the 1130 panel, were misplaced slightly. I realigned all the sockets and properly placed the register 2 bits 4 and 5 components.

Next< looked over the detailed signal and power routing, finding many suboptimal layouts that I could improve by manually routing traces. In many cases, signals were routed on the bottom side of the board and vias placed to move the signal between top and bottom, when there was a direct top side routing possible.

|

| Right side is autorouted with extraneous use of vias, left side is hand routed alternative |

I was able to remove most of the vias (through holes that conduct a signal from one layer to another). I also bumped up the trace width of the power lines (from the anode of the thyristor (big pad) to the 2 pin header that connects to the lamps. Now satisfied with how the board is configured, I printed an actual size copy on paper and verified alignment inside the 1130 pedestal panel.

Vertical clearance will be tight, requiring the board to be tilted to get inside the pedestal box, but will fit in place with enough room to work properly I think. I will measure the height inside the box precisely as a cross check. I did compensate by every so slightly shrinking the height of the board, taking a smidgen off the top and bottom margins and even a bit off the left edge.

|

| Final layout for the PCB that drives the 16 x 6 register display |

I also test fitted the actual thyristor and resistor parts on the paper copy to be sure that I didn't make a stupid error. Those appear fine as well, giving me adequate clearance between physical parts. The thyristor, resistor, turret connectors and 1 pin headers all fit on the top surface of the board, while the 2 pin headers are placed on the bottom side with only their pins sticking up for soldering on the top layer. The only soldering required on the bottom layer is for the 1 pin headers.

Since this is so tight, the order in which I solder everything will matter. I am not sure whether the resistor or the thyristor goes first, but the headers get soldered last. The turret connectors are fasted with nuts, not soldered, depending on mechanical pressure to make a good electrical connection.

With this presumably ready to ship off to the PCB manufacturer, I started in on the two boards that handle the remaining lamps inside the pedestal, each an 8 x 6 matrix of possible lamp positions. In practice, the 1130 does not use all 48 positions on either board, but I could lay this out symmetrically and omit components on the unused positions.

I copied and cut down the schematic and PCB files, before making the remaining adjustments necessary. There is not a wide free area for the three turret connectors, thus I will have to be clever about where I place them to have a usable board that can fit in the spots required.

In fact, I noticed that part of the bottom row of lamps is unused on both boards, so I simply removed row 6 columns 4, 5, 6 and 7. That gave me plenty of room to move the three turret connectors and still have a small board that will fit side by side where it has to inside the 1130 pedestal box.

|

| Small PCBs to implement the remaining lamps (other than the six major registers) |

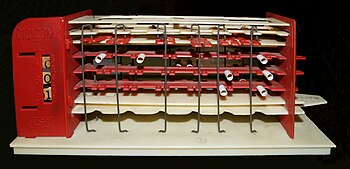

The pedestal box has a matrix of 5 x 5 plastic honeycomb units organized as two rows of seven blocks each. Horizontally, each hole may be used but vertically, only the odd numbered rows have lamps installed. Thus, the six rows of the panel sit on rows 1, 3 and 5 of the top honeycomb block then on 1, 3 and 5 of the bottom block.

|

| Honeycomb blocks (1 is missing in the picture) |

There are a total of 35 lamp positions horizontally across all the blocks, but only 30 are active. The registers sit in the rightmost 16 spots (viewed from the rear of the machine), thus take 3 whole honeycomb blocks plus on position of the next block. One open position sits to the left of the last register lamp, which is open space to accommodate the edges of my big and little PCB boards.

One of the small boards implements six lamp holes, the leftmost honeycomb plus one hole in the adjacent one. My board covers eight holes horizontally, however, so my board sits across two more hole positions in that adjacent block.

The block has two remaining hole positions, that will remain free or have just a smidgem of the small board edges over them. The other small board sits over the next eight hole positions, en entire block plus two holes of the block shared with the end of the big board.

Counting from left to right, in the rear, for the 35 possible lamp columns implemented by the seven honeycomb blocks, we have my first small board covering holes 1-8, the second small board covering holes 11 to 18, and the large board covering holes 20 to 35. The edges of the left two boards have holes 9 and 10 open and will have no problem fitting side by side.

The edges of the middle (small) and right (big) PCBs have just row 19 open to accommodate them, but that is sufficient for them to fit side by side. There is 1" between the centers of the end lamps of the adjacent boards, but they have less than 1/2" of margin from the lamp on their edges.

I will remove the mini PCBs that are the original IBM mounting spots for thyristors and to which the bulb holders are fit, detaching the wires from the terminal blocks which feed them. This will be saved so that the machine could be restored to original condition if someone so desired.

The turret connectors arrived today, spurring me to purchase all the 2 pin sockets and header strips needed to finish the construction of the boards. I picked up paper straws, which I will use as a barrel to hold the miniature light bulbs soldered onto their 2 pin headers so they can be plugged into the sockets on the boards.

Next up, I shipped off the boards to the foundry, using PcbUnlimited.com to panelize them. I should get them in about two weeks. Nice high quality 4 layer boards that cost almost $250 including shipping.

I am excited enough about this that I will go out and begin removing the original holders right now. I do have to separate out all the bulb holders, because once I have the headers and straws I can remove the bulbs and begin assembling all the plug-in lights.