SWISS ARMY KNIFE OF TIME DELAY RELAYS BEING USED

This device cost just over $22 and provides a very wide range of solutions, including of course the 90 to 100 second turn on delay we need for the IBM 1130 internal disk drive. The drive provides a choice of

- Turn on with a set delay after power is applied

- Turn on for a fixed duration when power is applied

- Repeatedly alternate on and off for equal durations, starting off

- Repeatedly alternate on and off for equal durations, starting on

- After a trigger signal, wait for a set duration then turn off

- A trigger signal turns it on for a set time, then off

- At the end of a trigger signal, turns on for a set time, then off

- Trigger signal turns on with set delay, then same delay before turning off

- Alternatively latch on or off upon each trigger signal

- Pulse on after a set delay when power applied, for a 0.5 second duration

Provides continuously variable delay setting in ten ranges from 0.1s to 10 days

Is powered by 12 to 240V of DC or AC at 50 or 60 Hz.

Comes with either SPDT or DPDT contacts.

I am using it with 48V DC, in the first mode, set to 100 seconds. I only need a single pole normally closed switch. Super overkill but cheaper than buying a used time delay that is just the functionality I needed.

WIRED IN AND TESTED, MOUNTED PERMANENTLY

The relay is installed and works properly - I get 98 seconds delay, which is right in the 90 to 100 second zone from the documentation. It sits nicely inside the power box.

INVESTIGATING RESISTANCE IN THE MOTOR ON CIRCUIT

Since the scope showed an 8V voltage drop across a pair of switches in the motor turn on circuit, I checked them out with a meter and the resistance was really low. I pulled the PCB that the wire connects into and the voltage still popped up to 8. Finally, I happened to check that a fat wire jumper was good and found 3.5K between the terminals involved!

ALD SEEMED TO MATCH THE POWER STRIP WIRING, BUT IT DIDN'T

The wiring of the power terminal block in the ALD shows a jumper between terminals 4 and 6, installed on IBM 1130 systems. When I looked at the terminal block on the machine, there appeared to be a fat jumper right where the ALD showed it.

That certainly looks like a jumper, but it isn't. When I measured between terminals 4 and 6, it was 3.5K. I removed the screws to measure the jumper by itself and that is when I discovered that it is not a jumper. It is a ground wire screwed into the metal base on its underside and hooked to terminal 4.

If you look closely it is obvious, but when viewing from somewhat above, it really looked like a U shaped jumper between the two terminals. The connection between the two terminals must be completed back inside the IBM 1130, although the ALD certainly makes it look like it happens here on the terminal block.

I whipped up a jumper, added it to the wires already present there, and was ready to test. I set up the scope to monitor the -Drive Motor On signal to see if it now sat down at ground level, then look at the Integrator and ramp generator/detector relative timing. In particular I wanted to be sure the 70 percent latch didn't turn on.

While I was looking at signal, 98 seconds elapsed and I heard the clang of the head loading solenoid activating! A quick probe of the -File Ready signal showed the drive happy and ready to accept commands.

USING CE SWITCHES TO MOVE THE ARM IN AND OUT

I tried the switches, asking to move the arm 20 mils inward toward the center of the platter and saw it move! I tried both 10 and 20 mil steps, forward and reverse movement, with success at each attempt. Holding down the continuous step switch produced a satisfying buzz as the drive moved about 100 tracks forward and then back. It is apparent that the 70 percent latch was what was blocking arm movement before this.

RETESTED EMERGENCY RETRACT, THIS TIME SUCCESSFULLY

The logic in the disk drive looks at the status of the Home microswitch which senses if the arm is at track 0. If not, when DC power is turned on, the arm should move backwards repeatedly until it reaches home. With the power off, I moved the arm out away from home and then activated the 48V supply. The arm backed right up.

TAPPING HOME SWITCH PRODUCES A FEW REVERSE MOVEMENT ATTEMPTS.

I noticed that every once in a while the arm would make a single seek attempt while it was sitting at home. I tried wiggling the wires and back of the microswitch, which would cause the attempts. I suspect that there is a contact that needs cleaning there.

MUCH IS WORKING CORRECTLY ON THE DRIVE

The drive does its startup and power down, emergency retraction, emits the sector and index pulses properly, goes into File Ready state after the 98 second delay and head loading, and moves in and out on command.

WORK AHEAD TO FINISH THE DISK DRIVE

I have to repair the connector for the one disk head, remount both of them after cleaning them really well, and try to fly the on a cartridge. The cartridge itself will need a really good cleaning as well before I even make the attempt.

Aligning the heads involves moving them slightly inward with an adjustment screw while watching a signal pattern on an oscilloscope. A special pattern is recorded on the Customer Engineer (CE) cartridge for this purpose, where the track is recorded in a special eccentric path.

An adapter substitutes the erase coil for the read/write coil because the erase coil is only sensitive to the two outer sections of a track, not the center. The read/write head records a wide track and the erase head trims away the outer bands to make the remaining signal narrow. Thus, the erase head poles are only focused on the outer edges - the curb and not the street.

With the eccentric path on the CE cartridge, the track is oscillating inward and outward of the centerline of the current head position. When the amount of signal detected on one pole is the same as the amount detected on the other pole, the head is properly centered between the eccentric extremes.

When the heads are aligned, I can watch the signal produced by the read electronics to validate much of the remaining electronics. All of these steps can be done without connecting the drive to the IBM 1130. Writing, however, is not permitted with the cable disconnected so that will have to wait until I reinstall the drive inside the 1130 cabinet.

BIG RESISTORS ARRIVED, FINISHED REPAIR OF 35V REGULATOR BOARD IN DRIVE

NEW PCBS FOR REPLACEMENT 6223 CARD THAT INTERFACES 1627 PLOTTER

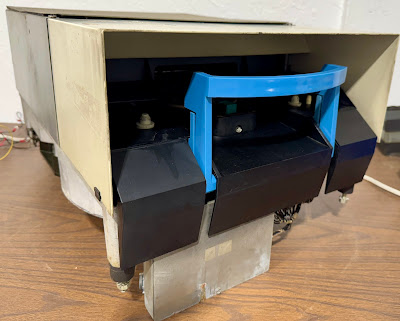

I got my components and the PCB blanks for the final version today. Before I solder together one of these, I decided to finish up the original with its bodge wiring, since it is working properly as far as all my bench testing is concerned. I drilled holes in the donor SLT card, soldered all the jumper wires between my PCB and donor card, then connected it with plastic screws and nuts.

I will put a scope on the 1130 output pins, with my replacement card inserted, and run some test programs to make sure that the output to the plotter is correct and the response to the 1130 works as well. Perhaps I will even fire up the 1627 plotter carcass to verify the servo motors move under the commands, if I feel ambitious.