FOCUSING ON TIMING OF SEEK CONTROL SIGNALS

The disk drive receives three signals from the 1130 disk controller logic:

- Access Drive (Access Go)

- Access 10-20 Mil Step

- Access Direction

The drive sends back a signal Access Ready that indicates when it can accept a seek request and shows the progress of the seek (crudely). Roughly, the Access Ready signal is true when the drive becomes ready and will switch to false about 5 ms after the seek begins, returning to true in a further 10 ms.

The disk drive logic manuals describe Access Go as a brief pulse. Since it is inverted logic, -Access Go drops from high to low briefly to request a seek. The wiring diagram for the 1130 shows that -Access Go on the drive is directly connected to -Access Drive in the 1130 controller logic.

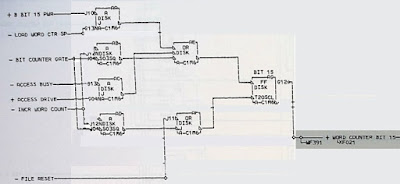

The problem with the above is that the logic producing -Access Drive does not generate a pulse. It asserts the signal by making -Access Go low when the +Access Busy signal goes high at the same time that +Access Ready is high and -Full Word Count is high.

The +Access Busy flipflop is switched on during an XIO Control (seek) instruction at time T6 as long as the count of cylinders to be traversed is not zero. The condition -Full Word Count is high when the cylinder count is non-zero, reaching zero when the final movement of the arm exhausts the requested number of cylinders to move.

+Access Busy stays on for the entire length of a seek request, while +Access Ready turns on and off with each 1 or 2 cylinder step taken by the disk drive. That is because the drive only knows how to move 1 cylinder (10 mils) or 2 cylinders (20 mils), forward or in reverse. The +Access Go is sent to trigger each step, with the cylinder count decrementing until we complete the transfer such that -Full Word Count goes low.

As long as +Access Busy is on (not done with the seek command) and -Full Word Count is high, we will repeatedly trigger the -Access Drive signal, each time it make the disk drive take another step. This happens because +Access Ready is high. When +Access Ready goes low in the midst of the step, it turns off the -Access Drive signal.

The disk drive is causing the alternation of the -Access Drive signal is the feedback signal from the disk drive, +Access Ready. When +Access Ready is high, we retrigger the next step until the full word count (cylinder count) is reached. When +Access Ready is low, we reset the -Access Drive signal.

The timing of +Access Ready from the disk drive has it go low about 5 milliseconds after the drive accepts a step request (i.e. -Access Go becomes low). It remains low for another 10 milliseconds then returns to high. The time to go low varies depending on whether this is a 10 mil (1 cylinder) or 20 mil (2 cylinder) step.

If we issue an XIO Control (seek) for 7 cylinders total, the word count is set to 7 initially. The controller logic sees an odd count thus it initially requests a 10 mil step. The word count is reduced by 1 and the step size now reverts to 20 mil for all further steps. Thus the word count first drops to 6, then is decremented by 2 on each step until the count gets to zero where our -Access Go is no longer issued. An even cylinder count begins and continues with 20 mil step sizes.

The timing chart for the disk drive has a brief pulse for -Access Go while we see from the controller logic side that instead it does low for about 5ms and then returns to high.

The state of the +Access Direction and +Access 10/20 Mil Step signals is shown as changing simultaneously with the supposed -Access Go pulse. The notion of simultaneous is a bit slippery when dealing with signals in an 1130, where everything is a bit asynchronous and not based on clocked flipflops like modern designs.

The +Access Direction signal is set or reset during the execution of an XIO Control based on bit 13 of word 2 of the Input Output Control Command (IOCC). That means at clock step T6 of the XIO step E1 the flipflop below is set and it is only changed at the next XIO Control, thus it remains constant through the course of an entire seek operation.

The +Access 10-20 Mil Step signal is generated from the word count register - it is the same as the low bit (bit 15) of the register. During the XIO Control step E2, at clock time T4, the cylinder count is loaded into the word count register.

The bits are inverted - thus a count of two (0000 0000 0000 0010) would load as (1111 1111 1111 1101). It looks at the B register (Storage Buffer Register) and when the bit is 0, the word count register bit is turned on.

The very first time that -Access Go turns off during a seek, bit 15 is forced on. Thus, if the low order bit of the seek request - B bit 15 - was 1, for an odd count, the word count register starts off with its bit 15 set to 0 but after the first step it is forced to 1 and stays that way. Word count register bit 15 is interpreted as +Access 10-20 Mil Step, when it is 0, the step is 10 mil and after it is forced to 1 the step size is 20 mil.

Thus, +Access 10-20 Mil Step will change when -Access Go is turned off, which is due to +Access Ready from the disk drive becoming false. It initially changes when the XIO Control command is being processed and then changes either once after the first step or stays constant for the duration of the seek command.

HOW THIS MAY IMPACT MY FPGA LOGIC IN THE V2315CF

This compares poorly to the timing shown in the disk drive documentation, which implies that the direction and step size signals change simultaneously with pulses on -Access Go. My logic was based on the documentation for the disk, but I can see some weaknesses based on what I discovered and documented above.

+Access Direction should be captured before the -Access Go signal goes low to start the timing of a step. I shouldn't see it change until the next XIO Control is issued. +Access 10-20 Mil Step will be set before the first -Access Go step and may change at the end of the first such step, before the next step is requested. I should capture the change while -Access Go is high and not change it until we finish a step of the arm.

My earlier logic for the state machine looked for edges on the +Access Ready and -Access Go signals, but the logic of the controller moves grossly based on the ~5ms and ~15ms timing of +Access Ready. I don't know whether it is possible to get glitches on those signals, as their timing should move on a relatively glacial scale. I may slightly debounce them in addition to passing them through a metastability chain of flipflops.

One final consequence of the way the logic functions is that when +Access Ready returns to high, the controller logic is going to be asserting -Access Go fairly quickly and I need to be ready to trigger off it. I am fairly certain that I already did this properly, but will double check.

No comments:

Post a Comment