ROLE OF POWER SUPPLY BOX

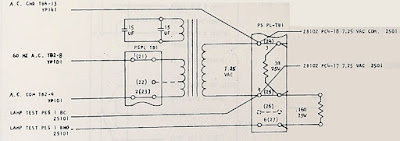

This box is connected to 115VAC, 208/230VAC, +6VDC, and 24VAC supplied over the power cable from the IBM 1130 system. It produces 48VDC to drive the solenoids such as the printer hammers and 20VAC to light the lamp for the encoder wheel. It provides a utility outlet typically used to connect an oscilloscope. It contains a usage meter with its control box that outputs 41VAC to turn the meter.

The printer has a blower motor to cool the SLT electronics card cage, a carriage motor to advance the paper through the printer, and a main drive motor that spins the print wheels and character encoder wheel. Various switches and relays control power to the motors and parts of the power supply.

In the 1130 system, a 24VAC circuit is routed to every frame in the system when the main console power switch is turned on. This voltage closes relays to power up the boxes. On the 1132, it activates relay K2 and contactor K1. K2 drains the voltage from the 48V power supply when the 1130 system power is off, preventing any printer solenoids from firing. K1 passes the incoming 208/230VAC from the CE power switch on the front panel of the 1132.

When the 1130 system is plugged into the building power, the utility outlet receives power even though the 1130 system is powered down. When the 1130 main power switch is turned on, the fans in all the peripherals begin to run because DC power rails are energizing the SLT logic cards in all peripherals. It energizes relays and contactors such as K1 and K2 in the printer. On the 1132, the motor power switch on the printer front panel must be switched on to start the two motors and provide power to the 48VDC and 20VAC power supplies.

REMOVAL OF POWER SUPPLY BOX

|

| Rear of printer |

|

| Front of printer |

There are two terminal strips - one on the rear and one on the left side of the power supply box. The wires need to be disconnected from each of these, after taking a picture to record the connections. The box itself is held down by four bolts, two across the front and two cross the rear.

The usage meter power/control box is separate, secured to the base by two screws. A medium size PCB sits on the right rear with three edge connectors around the periphery. It has the eight silicon controlled rectifiers (SCRs) and associated circuits to latch when a carriage control brush contacts the drum over which the carriage control tape passes. It also has some reed relays to handle the start and stop of carriage movement.

|

| Meter power/control box on left |

On other peripherals the utility socket (US 115V wall socket) is on the power box, but it sits in a separate small box in the 1132. All the wiring up to the carriage motor and main power switch runs alongside the utility outlet box.

Once I have all the wires disconnected, the box will be moved over to the bench to test it thoroughly.

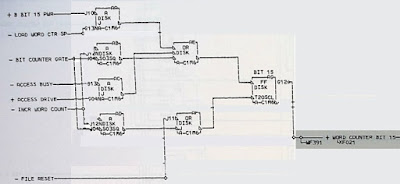

CONCERNED ABOUT THE CONDITION OF THE SCRS IN THE PRINTER

The circuit board with the eight SCRs (one for each carriage control channel used in the 1132) raised some worries. All the other components on the board look superficially okay except for the SCR parts themselves. The cans have quite a bit of rust on their surface. There is the possibility these may need to be replaced if contamination has entered the device itself or rusted the leads from the package to the PCB.

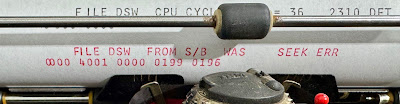

ADDENDUM ABOUT CARRIAGE CONTROL TAPE

IBM line printers use a carriage control tape, a loop of heavy paper that is suspended between two drums and moves in concert with the paper carriage. Across the width of the tape sit eight metal brushes. If there is a hole punched in the tape in the column where a given brush is riding, the SCR will detect the connection.

On the 1132 printer, there are brushes set up for columns 1, 2, 3, 4, 5, 6, 9 and 12. At any time, a programmer can test to see if there is a hole in the tape at the current line. The programmer can also request the carriage of the printer to skip forward, then stop the carriage when a particular column is detected.

On most IBM printers, the programmer simply asks the printer to skip to a given channel; the printer carriage moves until it reaches a line where the tape has a hole in the chosen channel. On the 1132 this is something the programmer or system software must accomplish because the 1132 does not have enough logic in it to be able to skip and stop on a target column.

By convention, column 1 is used to indicate the topmost line on a page of paper forms. The Forms Feed or similar button will skip the carriage until there is a hole in channel 1. Also, by convention channel 12 is used to indicate the last usable line on a paper form. The other channels tend to be used with special forms, allowing a program to jump down to a section of the form - for instance after printing a customer name and address, jump down to the list of items being ordered.

|

| Explanation from IBM 403 manual |